CS/컴퓨터 구조

4장 : 기억장치 - (4) 기억장치 설계

infobox503

2024. 12. 11. 09:57

<요약>

- 기억장치 용량 늘리기

- 병렬연결

- 데이터 비트 늘림

- 직렬연결

- 주소 비트 늘림

- 병렬연결

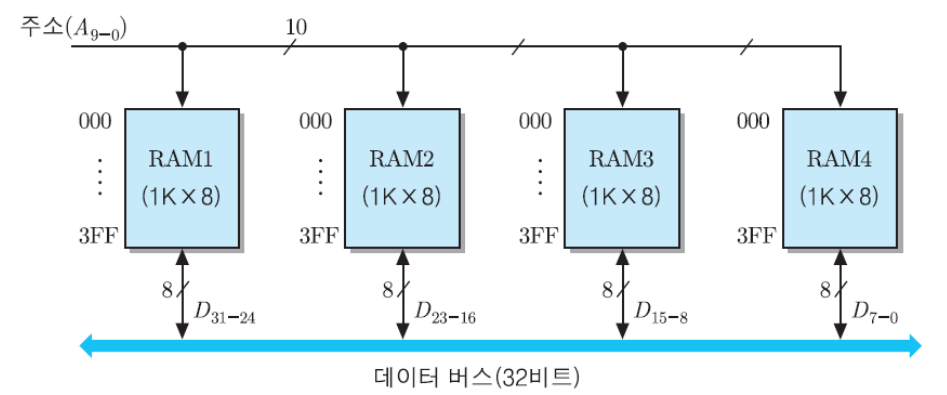

1. 기억장치 병렬연결

- 목적

- 데이터 비트 증가

- 예시

- 1K * 8bit RAM 소지

- 1K * 32bit 제작 목적

- ⇒ 1K * 8bit RAM 4개 병렬 연결

2. 기억장치 직렬연결

- 목적

- 주소 비트 증가

- 예시

- 16*4bit RAM 소지

- 32*4bit 제작

- ⇒ 16*4bit RAM 직렬 연결

- 직렬연결 방법

- 입력 신호를 1개 더 만듦

- CS 신호

- 해당 신호로 RAM 중에 1개를 선택

- 예시

- A4 = CS

- A4 신호로 RAM 중에 1개 선택해서 사용

- ⇒ RAM1 = 00000~01111

- ⇒ RAM2 = 10000~11111

- (맨 왼쪽 비트는 A4)

- 입력 신호를 1개 더 만듦

- 14p 문제 추천

3. 캐시 메모리

- 의미

- CPU ↔ 기억장치 사이의 속도 차이 완화

- 임시 저장 장치?

- 과정

- CPU ↔ 캐시 메모리 ↔ 주기억장치

- 특징

- 주기억장치 조회 시, 해당 내용이 캐시 메모리에 적재

- 캐시 메모리에 데이터가 있다면 주기억장치 조회X

- 캐시 메모리는 SRAM 사용(액세스 속도 빠름)