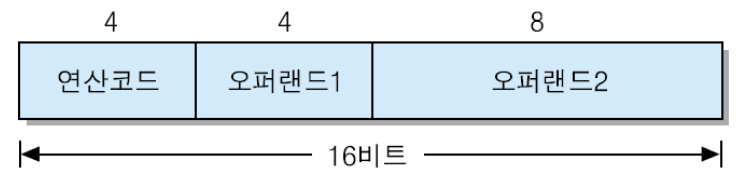

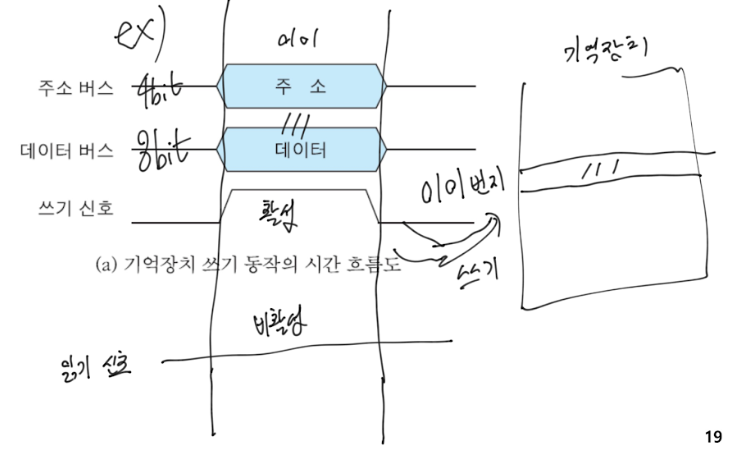

ALU구성 요소산술 연산장치논리 연산장치시프트 레지스터보수기상태 레지스터진수 보수 표현종류부호화-크기 표현1의 보수2의 보수비트 확장종류부호화-크기 비트 확장2의 보수 비트 확장논리 연산기본 논리 연산응용 논리 연산종류선택적-세트 연산선택적-보수 연산마스크 연산삽입 연산비교 연산시프트 연산자논리적 시프트순환 시프트데이터 전송 방법순환 시프트 + 논리적 시프트산술적 시프트논리적 시프트 사용C 플래그를 포함한 시프트 연산종류SHLCSHRCRLCRRC예외우측 시프트 연산해결 방안C 플래그가 레지스터로 못 넘어오게 막음오버플로우 알림1. ALUALU(산술논리연산장치)산술, 논리 연산 수행CPU 내부 존재구성 요소산술 연산장치사칙연산 수행논리 연산장치AND, NOT 등 수행시프트 레지스터비트를 왼, 오로 이동보수..